Biraz uzunca aradan sonra bu yazıda Altera DE2-115 adında TERASIC firmasının hazırlamış olduğu eğitim platformu ile VGA video çıkışının nasıl yapılabildiğini göreceğiz.

Öncelikle VGA sinyalinin tarihçesine bakalım.Video Graphics Array veya VGA (Türkçe: Video Grafik Dizisi[1]), bilgisayarlardaki analog görüntü standardı ile 15-pin D-sub konnektörü veya 640×480 çözünürlüğün kendisini ifade eder. İlk defa 1988 yılında IBM tarafından piyasaya sürüldü.

VGA bağlantısı, göreceli olarak eski bir teknoloji olmasına rağman 2010 yılında hala önemli bir bağlantı standardı olma özelliğini koruyor. Fakat günümüzde performans, kalite ve kolaylık bakımından yetersiz olduğu düşünülmektedir. Büyük bilgisayar şirketleri VGA standardını terk etme planları hazırlamaya başlamıştır. (tr.wikipedia.org)

Şimdi de VGA sinyalinin ne gibi bir sinyal olduğundan bahsedeyim. Bu sinyal yaygın olarak bilgisayar monitörlerinde görüntü oluşturulması için kullanılan bir protokoldür. Temel olarak hat üzerinde RGB yani, Kırmızı,Yeşil ,Mavi renk bilgisini taşıyan üç hat ve iki tane senkronizasyon sinyali bulunur. Burada senkronizasyon sinyali ekrandaki tarama noktalarının konumunu ve pixel frekanslarını belirlemektedir.

Bu uygulamada yaygın kullanılan düşük çözünürlük uygulamaların aksine biraz daha iyi sayılabilecek 800×600 boyutlarında bir görüntü kontrolcüsü göreceksiniz.

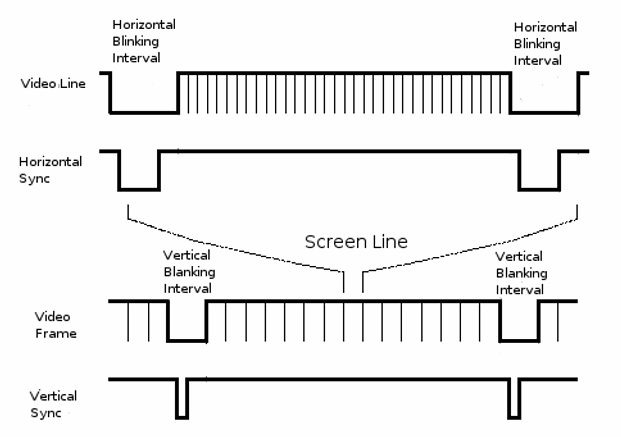

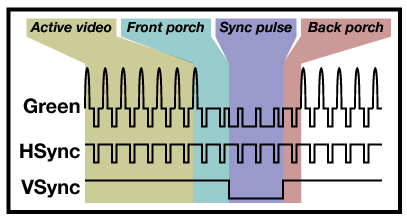

Yukarıda görmakte olduğunuz bir VGA sinyalinin zamanlama diyagramı görüntüsüdür. Burada belirtilen horizontal sync sinyali yani yatay senkron sinyali, görüntünün ekranı tararken yataydaki bir satırın senkronizasyonu için(Yazının devamında h_sync diye anılacaktır.), vertical sync sinyali ise taramanın bitip başa dönmesi gereken sürenin belirlenmesi için gerekli olan dikey senkronizasyon sinyalidir.(Yazının devamında v_sync sinyali olarak anılacaktır.)

Dikkat edilirse h_sync sinyali her satır için gelmekte, v_sync sinyali ise satırların tümü bittiğinde gelmektedir. Temel olarak VGA sinyali bunlardan ibarettir. Daha detaylı bilgiyi internetten temin edebilirsiniz.

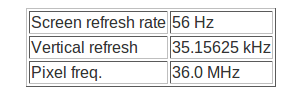

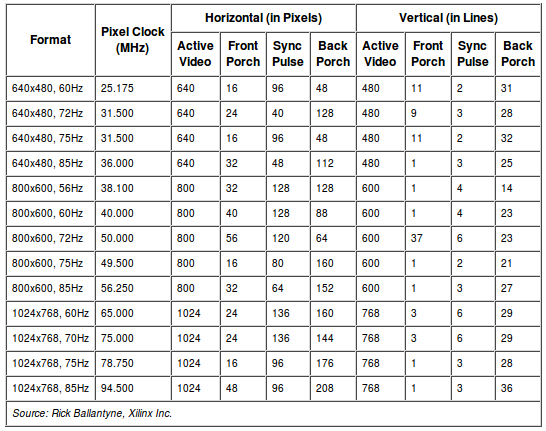

Şimdi bu aralıklarda bizim inceleyeceğimiz zamanlama bilgilerini verelim.

Temel olarak bizim kullanacağımız formatın temel bilgileri:

- Screen refresh rate = Ekran yenileme oranı. Saniyede ekranda kaç görüntü gösterileceğidir.

- Vertical refresh = Bir frame görüntünün dikey senkron sinyali frekansının ne olduğudur.

- Pixel freq.= Pixel frekansıdır. Ekrana saniyede yazılan pixel sayısını gösterir.

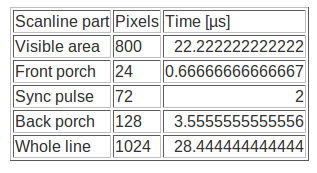

Bu uygulamada kullanılan h_sync sinyali için zamanlama bilgileri:

(Bu tablolarda gördüğünüz “front porch” ve “back porch” süreleri senkron sinyalleri öncesi yada sonrasında olması gereken bekleme süreleridir.)

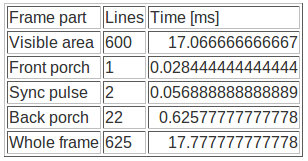

Bu uygulamada kullanılan v_sync sinyali için zamanlama bilgileri:

Bu zamanlamalar uygulandığında monitöre gidecek renk kanallarından birinin temsili olarak görünüşü:

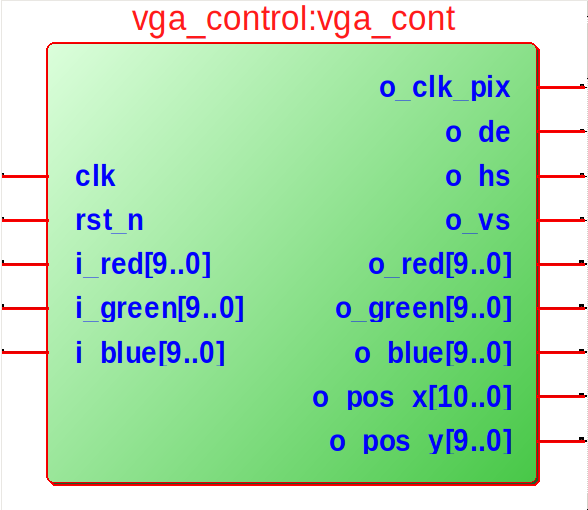

Artık yapacağımız modüllerle ilgili kısımlara geçebiliriz. Modülü aşağıdaki gibi düşünerek tasarladım.

*Modülde Clock sinyali ve Reset sinyali haricinde tüm girişlerin başında” i_” çıkışlarda ise “o_” bulunmaktadır. Clock ve Reset sinyali zaten giriş olacağından yazma gereği duymadım.

Bunun dışında module baktığımızda RGB sinyallerinden her bir giriş çıkışı 10 bit tanımladım. (Altera DE2-115 de sadece 8 pin bağlanmış.İsterseniz 8 bit yapabilirsiniz.) “o_de” sinyali FPGA üzerinde DAC entegresine girmemiz için gerekli olan Data Enable sinyalidir. Yani pixel bilgisi gönderdiğimiz aralıklarda lojik 1, göndermediğimiz zamanlarda lojik 0 olmaktadır. “o_pos_x – ..y” sinyalleri oyun gibi yada hangi pixel bilgisini yazdığı bilinmesi istenen uygulamalarda kullanılması amacı ile eklenmiştir. Geri kalan sinyaller isimlerinden anlaşılmaktadır.

Modülümüzün VHDL kodu aşağıdadır.

- --=================================================================

- -------------------------------------------------------------------

- -- Orhan YILMAZ

- -- VGA-Controler

- -- www.mafgom.com --

- -------------------------------------------------------------------

- --=================================================================

- LIBRARY ieee;

- use ieee.std_logic_1164.ALL;

- use ieee.std_logic_unsigned.all;

- use ieee.std_logic_arith.ALL;

-

- entity vga_control is

- port(

- --Clock,Reset Signal's ports

- clk :in std_logic;

- rst_n :in std_logic;

-

- --Input RGB Signal's ports

- i_red :in std_logic_vector(9 downto 0);

- i_green :in std_logic_vector(9 downto 0);

- i_blue :in std_logic_vector(9 downto 0);

-

- --Output RGB Signal's ports

- o_red :out std_logic_vector(9 downto 0);

- o_green :out std_logic_vector(9 downto 0);

- o_blue :out std_logic_vector(9 downto 0);

-

- --Output Position value

- o_pos_x :out std_logic_vector(10 downto 0);

- o_pos_y :out std_logic_vector( 9 downto 0);

-

- --Output Synchronous Signal's pins

- o_vs :out std_logic;

- o_hs :out std_logic;

- o_clk_pix :out std_logic;

- o_de :out std_logic

- );

- end entity;

-

- architecture RTL_VGA of vga_control is

-

- signal count_h : std_logic_vector(10 downto 0):= (OTHERS =>'0'); --MAX "10000000000"(1024)

- signal count_v : std_logic_vector( 9 downto 0):= (OTHERS =>'0'); --MAX "1001110001"(625)

-

- constant h_active : std_logic_vector( 9 downto 0):= "1100100000"; --800

- constant h_front_porch : std_logic_vector( 4 downto 0):= "11000"; --24

- constant h_sync : std_logic_vector( 6 downto 0):= "1001000"; --72

- constant h_back_porch : std_logic_vector( 7 downto 0):= "10000000"; --128

- constant h_total : std_logic_vector( 9 downto 0):= "1111111111"; --1024

-

- constant v_active : std_logic_vector( 9 downto 0):= "1100100000"; --600

- constant v_front_porch : std_logic := '1'; --1

- constant v_sync : std_logic_vector( 1 downto 0):= "10"; --2

- constant v_back_porch : std_logic_vector( 4 downto 0):= "10110"; --22

- constant v_total : std_logic_vector( 9 downto 0):= "1001110000"; --625

-

- signal count_de_depth : std_logic_vector(10 downto 0):= (OTHERS => '0');

- signal de : std_logic := '0';

- signal h_blank : std_logic_vector(7 downto 0):= (OTHERS => '0');

- signal v_blank : std_logic_vector(4 downto 0):= (OTHERS => '0');

- signal vs : std_logic := '1';

-

- begin

-

- h_blank <= h_sync + h_back_porch;

- v_blank <= v_sync + v_back_porch;

-

- --Vertical Counter Generated

- count_v_p:process(clk,rst_n)

- begin

- if(rst_n = '0') then

- count_v <= (OTHERS=>'0');

- elsif(clk = '1' and clk'event) then

- if(count_v < v_total) then

- if(count_h = h_total) then

- count_v <= count_v + '1';

- end if;

- else

- count_v <= (OTHERS=>'0');

- end if;

- end if;

- end process;

-

- --Horizontal Counter Generated

- count_h_p:process(clk,rst_n)

- begin

- if(rst_n = '0') then

- count_h <= (OTHERS=>'0');

- elsif(clk = '1' and clk'event) then

- if(count_h < h_total) then

- count_h <= count_h + '1';

- else

- count_h <= (OTHERS=>'0');

- end if;

- end if;

- end process;

-

- --VS Generated

- vs_p:process(clk,rst_n)

- begin

- if(rst_n = '0') then

- vs <= '1';

- elsif(clk = '1' and clk'event) then

- if(count_v = "0") then --(v_front_porch - '1')) then

- if(count_h = h_front_porch + h_sync -"10") then

- vs <= '0';

- end if;

- elsif(count_v = v_front_porch + v_sync - '1') then

- if(count_h = h_front_porch + h_sync - "10") then

- vs <= '1';

- end if;

- end if;

- end if;

- end process;

-

- --VSYNC Generated

- vs_o_p:process(clk,rst_n)

- begin

- if(rst_n = '0') then

- o_vs <= '1';

- elsif(clk = '1' and clk'event) then

- o_vs <= vs;

- end if;

- end process;

-

- --HSYNC Generated

- hs_o_p:process(clk,rst_n)

- begin

- if(rst_n = '0') then

- o_hs <= '1';

- elsif(clk = '1' and clk'event) then

- if(count_h = h_front_porch - '1')then

- o_hs <= '0';

- elsif(count_h = h_front_porch + h_sync - '1') then

- o_hs <= '1';

- end if;

- end if;

- end process;

-

- --Output Data Enable Generated

- de_o_p:process(clk,rst_n)

- begin

- if(rst_n = '0') then

- o_de <= '0';

- elsif(clk = '1' and clk'event) then

- if(vs = '1') then

- if(count_h = h_back_porch + h_sync - '1') then

- o_de <= '1';

- elsif(count_h = h_total - h_front_porch) then

- o_de <= '0';

- end if;

- else

- o_de <= '0';

- end if;

- end if;

- end process;

-

- --Data Enable Generated

- de_p:process(clk,rst_n)

- begin

- if(rst_n = '0') then

- de <= '0';

- elsif(clk = '1' and clk'event) then

- if( vs = '1') then

- if(count_h = h_back_porch + h_sync - '1') then

- de <= '1';

- elsif(count_h = h_total - h_front_porch) then

- de<='0';

- end if;

- else

- de <= '0';

- end if;

- end if;

- end process;

-

- --Data Enable Depth counter

- count_de_depth_p:process(clk,rst_n)

- begin

- if(rst_n = '0') then

- count_de_depth <= (OTHERS => '0');

- elsif(clk = '1' and clk'event) then

- if(de = '1') then

- count_de_depth <= count_de_depth + '1';

- else

- count_de_depth <= (OTHERS => '0');

- end if;

- end if;

- end process;

-

- -- Output RGB Signas

- o_red <= i_red when de = '1' else (OTHERS => '0');

- o_green <= i_green when de = '1' else (OTHERS => '0');

- o_blue <= i_blue when de = '1' else (OTHERS => '0');

-

- --Output Pixel Clock

- o_clk_pix <= clk when rst_n = '1' else '0';

-

- --Output Position Value

- o_pos_x <= (count_h - h_blank) when de = '1' and count_h >= h_blank else (OTHERS => '0');

- o_pos_y <= (count_v - "10" ) when de = '1' and count_v >= "10" else (OTHERS => '0');

-

- end RTL_VGA;

Not: Top modül için yani bu kodun FPGA üzerine yüklenerek çalıştırılması için , Quartus programında tools sekmesi altında bulunan MegaWizard ile bir PLL modülü oluşturmanız gerekmektedir. Gerekli olan frekans pixel frekansımızdır. Yani modülümüzün clk girişine en üstte belirtirldiği gibi 36Mhz pixel clk girmeniz gerekecek.

Modülü diğer modüllerin altında kullanmak için kompanent tanımlamamız gerekiyor. Ben ayrı bir dosyada tanımlayıp kullanıyorum. Sizde canınız nasıl isterse öyle kullanabilirsiniz.

- -------------------------------------------------------------------

- -- Orhan YILMAZ

- -- VGA-Controler Component Package

- -- www.mafgom.com

- -------------------------------------------------------------------

- --=================================================================

- LIBRARY ieee;

- use ieee.std_logic_1164.ALL;

- use ieee.std_logic_unsigned.all;

- use ieee.std_logic_arith.ALL;

-

- package pkg_vga_component is

-

- component vga_control is

- port(

- --Clock,Reset Signal's ports

- clk :in std_logic;

- rst_n :in std_logic;

-

- --Input RGB Signal's ports

- i_red :in std_logic_vector(9 downto 0);

- i_green :in std_logic_vector(9 downto 0);

- i_blue :in std_logic_vector(9 downto 0);

-

- --Output RGB Signal's ports

- o_red :out std_logic_vector(9 downto 0);

- o_green :out std_logic_vector(9 downto 0);

- o_blue :out std_logic_vector(9 downto 0);

-

- --Output Position value

- o_pos_x :out std_logic_vector(10 downto 0);

- o_pos_y :out std_logic_vector( 9 downto 0);

-

- --Output Synchronous Signal's pins

- o_vs :out std_logic;

- o_hs :out std_logic;

- o_clk_pix :out std_logic;

- o_de :out std_logic

- );

- end component;

-

- end package;

Benim oluşturduğum PLL modülü:

- -- megafunction wizard: %ALTPLL%

- -- GENERATION: STANDARD

- -- VERSION: WM1.0

- -- MODULE: altpll

-

- -- ============================================================

- -- File Name: pll_36mhz.vhd

- -- Megafunction Name(s):

- -- altpll

- --

- -- Simulation Library Files(s):

- -- altera_mf

- -- ============================================================

- -- ************************************************************

- -- THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!

- --

- -- 11.0 Build 157 04/27/2011 SJ Web Edition

- -- ************************************************************

-

- --Copyright (C) 1991-2011 Altera Corporation

- --Your use of Altera Corporation's design tools, logic functions

- --and other software and tools, and its AMPP partner logic

- --functions, and any output files from any of the foregoing

- --(including device programming or simulation files), and any

- --associated documentation or information are expressly subject

- --to the terms and conditions of the Altera Program License

- --Subscription Agreement, Altera MegaCore Function License

- --Agreement, or other applicable license agreement, including,

- --without limitation, that your use is for the sole purpose of

- --programming logic devices manufactured by Altera and sold by

- --Altera or its authorized distributors. Please refer to the

- --applicable agreement for further details.

-

- LIBRARY ieee;

- USE ieee.std_logic_1164.all;

-

- LIBRARY altera_mf;

- USE altera_mf.all;

-

- ENTITY pll_36mhz IS

- PORT

- (

- areset : IN STD_LOGIC := '0';

- inclk0 : IN STD_LOGIC := '0';

- c0 : OUT STD_LOGIC ;

- locked : OUT STD_LOGIC

- );

- END pll_36mhz;

-

- ARCHITECTURE SYN OF pll_36mhz IS

-

- SIGNAL sub_wire0 : STD_LOGIC ;

- SIGNAL sub_wire1 : STD_LOGIC_VECTOR (4 DOWNTO 0);

- SIGNAL sub_wire2 : STD_LOGIC ;

- SIGNAL sub_wire3 : STD_LOGIC ;

- SIGNAL sub_wire4 : STD_LOGIC_VECTOR (1 DOWNTO 0);

- SIGNAL sub_wire5_bv : BIT_VECTOR (0 DOWNTO 0);

- SIGNAL sub_wire5 : STD_LOGIC_VECTOR (0 DOWNTO 0);

-

- COMPONENT altpll

- GENERIC (

- bandwidth_type : STRING;

- clk0_divide_by : NATURAL;

- clk0_duty_cycle : NATURAL;

- clk0_multiply_by : NATURAL;

- clk0_phase_shift : STRING;

- compensate_clock : STRING;

- inclk0_input_frequency : NATURAL;

- intended_device_family : STRING;

- lpm_hint : STRING;

- lpm_type : STRING;

- operation_mode : STRING;

- pll_type : STRING;

- port_activeclock : STRING;

- port_areset : STRING;

- port_clkbad0 : STRING;

- port_clkbad1 : STRING;

- port_clkloss : STRING;

- port_clkswitch : STRING;

- port_configupdate : STRING;

- port_fbin : STRING;

- port_inclk0 : STRING;

- port_inclk1 : STRING;

- port_locked : STRING;

- port_pfdena : STRING;

- port_phasecounterselect : STRING;

- port_phasedone : STRING;

- port_phasestep : STRING;

- port_phaseupdown : STRING;

- port_pllena : STRING;

- port_scanaclr : STRING;

- port_scanclk : STRING;

- port_scanclkena : STRING;

- port_scandata : STRING;

- port_scandataout : STRING;

- port_scandone : STRING;

- port_scanread : STRING;

- port_scanwrite : STRING;

- port_clk0 : STRING;

- port_clk1 : STRING;

- port_clk2 : STRING;

- port_clk3 : STRING;

- port_clk4 : STRING;

- port_clk5 : STRING;

- port_clkena0 : STRING;

- port_clkena1 : STRING;

- port_clkena2 : STRING;

- port_clkena3 : STRING;

- port_clkena4 : STRING;

- port_clkena5 : STRING;

- port_extclk0 : STRING;

- port_extclk1 : STRING;

- port_extclk2 : STRING;

- port_extclk3 : STRING;

- self_reset_on_loss_lock : STRING;

- width_clock : NATURAL

- );

- PORT (

- areset : IN STD_LOGIC ;

- clk : OUT STD_LOGIC_VECTOR (4 DOWNTO 0);

- inclk : IN STD_LOGIC_VECTOR (1 DOWNTO 0);

- locked : OUT STD_LOGIC

- );

- END COMPONENT;

-

- BEGIN

- sub_wire5_bv(0 DOWNTO 0) <= "0";

- sub_wire5 <= To_stdlogicvector(sub_wire5_bv);

- locked <= sub_wire0;

- sub_wire2 <= sub_wire1(0);

- c0 <= sub_wire2;

- sub_wire3 <= inclk0;

- sub_wire4 <= sub_wire5(0 DOWNTO 0) & sub_wire3;

-

- altpll_component : altpll

- GENERIC MAP (

- bandwidth_type => "AUTO",

- clk0_divide_by => 25,

- clk0_duty_cycle => 50,

- clk0_multiply_by => 18,

- clk0_phase_shift => "0",

- compensate_clock => "CLK0",

- inclk0_input_frequency => 20000,

- intended_device_family => "Cyclone IV GX",

- lpm_hint => "CBX_MODULE_PREFIX=pll_36mhz",

- lpm_type => "altpll",

- operation_mode => "NORMAL",

- pll_type => "AUTO",

- port_activeclock => "PORT_UNUSED",

- port_areset => "PORT_USED",

- port_clkbad0 => "PORT_UNUSED",

- port_clkbad1 => "PORT_UNUSED",

- port_clkloss => "PORT_UNUSED",

- port_clkswitch => "PORT_UNUSED",

- port_configupdate => "PORT_UNUSED",

- port_fbin => "PORT_UNUSED",

- port_inclk0 => "PORT_USED",

- port_inclk1 => "PORT_UNUSED",

- port_locked => "PORT_USED",

- port_pfdena => "PORT_UNUSED",

- port_phasecounterselect => "PORT_UNUSED",

- port_phasedone => "PORT_UNUSED",

- port_phasestep => "PORT_UNUSED",

- port_phaseupdown => "PORT_UNUSED",

- port_pllena => "PORT_UNUSED",

- port_scanaclr => "PORT_UNUSED",

- port_scanclk => "PORT_UNUSED",

- port_scanclkena => "PORT_UNUSED",

- port_scandata => "PORT_UNUSED",

- port_scandataout => "PORT_UNUSED",

- port_scandone => "PORT_UNUSED",

- port_scanread => "PORT_UNUSED",

- port_scanwrite => "PORT_UNUSED",

- port_clk0 => "PORT_USED",

- port_clk1 => "PORT_UNUSED",

- port_clk2 => "PORT_UNUSED",

- port_clk3 => "PORT_UNUSED",

- port_clk4 => "PORT_UNUSED",

- port_clk5 => "PORT_UNUSED",

- port_clkena0 => "PORT_UNUSED",

- port_clkena1 => "PORT_UNUSED",

- port_clkena2 => "PORT_UNUSED",

- port_clkena3 => "PORT_UNUSED",

- port_clkena4 => "PORT_UNUSED",

- port_clkena5 => "PORT_UNUSED",

- port_extclk0 => "PORT_UNUSED",

- port_extclk1 => "PORT_UNUSED",

- port_extclk2 => "PORT_UNUSED",

- port_extclk3 => "PORT_UNUSED",

- self_reset_on_loss_lock => "OFF",

- width_clock => 5

- )

- PORT MAP (

- areset => areset,

- inclk => sub_wire4,

- locked => sub_wire0,

- clk => sub_wire1

- );

-

- END SYN;

-

- -- ============================================================

- -- CNX file retrieval info

- -- ============================================================

- -- Retrieval info: PRIVATE: ACTIVECLK_CHECK STRING "0"

- -- Retrieval info: PRIVATE: BANDWIDTH STRING "1.000"

- -- Retrieval info: PRIVATE: BANDWIDTH_FEATURE_ENABLED STRING "1"

- -- Retrieval info: PRIVATE: BANDWIDTH_FREQ_UNIT STRING "MHz"

- -- Retrieval info: PRIVATE: BANDWIDTH_PRESET STRING "Low"

- -- Retrieval info: PRIVATE: BANDWIDTH_USE_AUTO STRING "1"

- -- Retrieval info: PRIVATE: BANDWIDTH_USE_PRESET STRING "0"

- -- Retrieval info: PRIVATE: CLKBAD_SWITCHOVER_CHECK STRING "0"

- -- Retrieval info: PRIVATE: CLKLOSS_CHECK STRING "0"

- -- Retrieval info: PRIVATE: CLKSWITCH_CHECK STRING "0"

- -- Retrieval info: PRIVATE: CNX_NO_COMPENSATE_RADIO STRING "0"

- -- Retrieval info: PRIVATE: CREATE_CLKBAD_CHECK STRING "0"

- -- Retrieval info: PRIVATE: CREATE_INCLK1_CHECK STRING "0"

- -- Retrieval info: PRIVATE: CUR_DEDICATED_CLK STRING "c0"

- -- Retrieval info: PRIVATE: CUR_FBIN_CLK STRING "c0"

- -- Retrieval info: PRIVATE: DEVICE_SPEED_GRADE STRING "7"

- -- Retrieval info: PRIVATE: DIV_FACTOR0 NUMERIC "1"

- -- Retrieval info: PRIVATE: DUTY_CYCLE0 STRING "50.00000000"

- -- Retrieval info: PRIVATE: EFF_OUTPUT_FREQ_VALUE0 STRING "36.000000"

- -- Retrieval info: PRIVATE: EXPLICIT_SWITCHOVER_COUNTER STRING "0"

- -- Retrieval info: PRIVATE: EXT_FEEDBACK_RADIO STRING "0"

- -- Retrieval info: PRIVATE: GLOCKED_COUNTER_EDIT_CHANGED STRING "1"

- -- Retrieval info: PRIVATE: GLOCKED_FEATURE_ENABLED STRING "0"

- -- Retrieval info: PRIVATE: GLOCKED_MODE_CHECK STRING "0"

- -- Retrieval info: PRIVATE: GLOCK_COUNTER_EDIT NUMERIC "1048575"

- -- Retrieval info: PRIVATE: HAS_MANUAL_SWITCHOVER STRING "1"

- -- Retrieval info: PRIVATE: INCLK0_FREQ_EDIT STRING "50.000"

- -- Retrieval info: PRIVATE: INCLK0_FREQ_UNIT_COMBO STRING "MHz"

- -- Retrieval info: PRIVATE: INCLK1_FREQ_EDIT STRING "100.000"

- -- Retrieval info: PRIVATE: INCLK1_FREQ_EDIT_CHANGED STRING "1"

- -- Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_CHANGED STRING "1"

- -- Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_COMBO STRING "MHz"

- -- Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone IV GX"

- -- Retrieval info: PRIVATE: INT_FEEDBACK__MODE_RADIO STRING "1"

- -- Retrieval info: PRIVATE: LOCKED_OUTPUT_CHECK STRING "1"

- -- Retrieval info: PRIVATE: LONG_SCAN_RADIO STRING "1"

- -- Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE STRING "Not Available"

- -- Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE_DIRTY NUMERIC "0"

- -- Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT0 STRING "deg"

- -- Retrieval info: PRIVATE: MIG_DEVICE_SPEED_GRADE STRING "Any"

- -- Retrieval info: PRIVATE: MIRROR_CLK0 STRING "0"

- -- Retrieval info: PRIVATE: MULT_FACTOR0 NUMERIC "1"

- -- Retrieval info: PRIVATE: NORMAL_MODE_RADIO STRING "1"

- -- Retrieval info: PRIVATE: OUTPUT_FREQ0 STRING "36.00000000"

- -- Retrieval info: PRIVATE: OUTPUT_FREQ_MODE0 STRING "1"

- -- Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT0 STRING "MHz"

- -- Retrieval info: PRIVATE: PHASE_RECONFIG_FEATURE_ENABLED STRING "1"

- -- Retrieval info: PRIVATE: PHASE_RECONFIG_INPUTS_CHECK STRING "0"

- -- Retrieval info: PRIVATE: PHASE_SHIFT0 STRING "0.00000000"

- -- Retrieval info: PRIVATE: PHASE_SHIFT_STEP_ENABLED_CHECK STRING "0"

- -- Retrieval info: PRIVATE: PHASE_SHIFT_UNIT0 STRING "deg"

- -- Retrieval info: PRIVATE: PLL_ADVANCED_PARAM_CHECK STRING "0"

- -- Retrieval info: PRIVATE: PLL_ARESET_CHECK STRING "1"

- -- Retrieval info: PRIVATE: PLL_AUTOPLL_CHECK NUMERIC "1"

- -- Retrieval info: PRIVATE: PLL_ENHPLL_CHECK NUMERIC "0"

- -- Retrieval info: PRIVATE: PLL_FASTPLL_CHECK NUMERIC "0"

- -- Retrieval info: PRIVATE: PLL_FBMIMIC_CHECK STRING "0"

- -- Retrieval info: PRIVATE: PLL_LVDS_PLL_CHECK NUMERIC "0"

- -- Retrieval info: PRIVATE: PLL_PFDENA_CHECK STRING "0"

- -- Retrieval info: PRIVATE: PLL_TARGET_HARCOPY_CHECK NUMERIC "0"

- -- Retrieval info: PRIVATE: PRIMARY_CLK_COMBO STRING "inclk0"

- -- Retrieval info: PRIVATE: RECONFIG_FILE STRING "pll_36mhz.mif"

- -- Retrieval info: PRIVATE: SACN_INPUTS_CHECK STRING "0"

- -- Retrieval info: PRIVATE: SCAN_FEATURE_ENABLED STRING "1"

- -- Retrieval info: PRIVATE: SELF_RESET_LOCK_LOSS STRING "0"

- -- Retrieval info: PRIVATE: SHORT_SCAN_RADIO STRING "0"

- -- Retrieval info: PRIVATE: SPREAD_FEATURE_ENABLED STRING "0"

- -- Retrieval info: PRIVATE: SPREAD_FREQ STRING "50.000"

- -- Retrieval info: PRIVATE: SPREAD_FREQ_UNIT STRING "KHz"

- -- Retrieval info: PRIVATE: SPREAD_PERCENT STRING "0.500"

- -- Retrieval info: PRIVATE: SPREAD_USE STRING "0"

- -- Retrieval info: PRIVATE: SRC_SYNCH_COMP_RADIO STRING "0"

- -- Retrieval info: PRIVATE: STICKY_CLK0 STRING "1"

- -- Retrieval info: PRIVATE: SWITCHOVER_COUNT_EDIT NUMERIC "1"

- -- Retrieval info: PRIVATE: SWITCHOVER_FEATURE_ENABLED STRING "1"

- -- Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0"

- -- Retrieval info: PRIVATE: USE_CLK0 STRING "1"

- -- Retrieval info: PRIVATE: USE_CLKENA0 STRING "0"

- -- Retrieval info: PRIVATE: USE_MIL_SPEED_GRADE NUMERIC "0"

- -- Retrieval info: PRIVATE: ZERO_DELAY_RADIO STRING "0"

- -- Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all

- -- Retrieval info: CONSTANT: BANDWIDTH_TYPE STRING "AUTO"

- -- Retrieval info: CONSTANT: CLK0_DIVIDE_BY NUMERIC "25"

- -- Retrieval info: CONSTANT: CLK0_DUTY_CYCLE NUMERIC "50"

- -- Retrieval info: CONSTANT: CLK0_MULTIPLY_BY NUMERIC "18"

- -- Retrieval info: CONSTANT: CLK0_PHASE_SHIFT STRING "0"

- -- Retrieval info: CONSTANT: COMPENSATE_CLOCK STRING "CLK0"

- -- Retrieval info: CONSTANT: INCLK0_INPUT_FREQUENCY NUMERIC "20000"

- -- Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone IV GX"

- -- Retrieval info: CONSTANT: LPM_TYPE STRING "altpll"

- -- Retrieval info: CONSTANT: OPERATION_MODE STRING "NORMAL"

- -- Retrieval info: CONSTANT: PLL_TYPE STRING "AUTO"

- -- Retrieval info: CONSTANT: PORT_ACTIVECLOCK STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_ARESET STRING "PORT_USED"

- -- Retrieval info: CONSTANT: PORT_CLKBAD0 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_CLKBAD1 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_CLKLOSS STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_CLKSWITCH STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_CONFIGUPDATE STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_FBIN STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_INCLK0 STRING "PORT_USED"

- -- Retrieval info: CONSTANT: PORT_INCLK1 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_LOCKED STRING "PORT_USED"

- -- Retrieval info: CONSTANT: PORT_PFDENA STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_PHASECOUNTERSELECT STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_PHASEDONE STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_PHASESTEP STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_PHASEUPDOWN STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_PLLENA STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_SCANACLR STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_SCANCLK STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_SCANCLKENA STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_SCANDATA STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_SCANDATAOUT STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_SCANDONE STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_SCANREAD STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_SCANWRITE STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clk0 STRING "PORT_USED"

- -- Retrieval info: CONSTANT: PORT_clk1 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clk2 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clk3 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clk4 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clk5 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clkena0 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clkena1 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clkena2 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clkena3 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clkena4 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_clkena5 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_extclk0 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_extclk1 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_extclk2 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: PORT_extclk3 STRING "PORT_UNUSED"

- -- Retrieval info: CONSTANT: SELF_RESET_ON_LOSS_LOCK STRING "OFF"

- -- Retrieval info: CONSTANT: WIDTH_CLOCK NUMERIC "5"

- -- Retrieval info: USED_PORT: @clk 0 0 5 0 OUTPUT_CLK_EXT VCC "@clk[4..0]"

- -- Retrieval info: USED_PORT: @inclk 0 0 2 0 INPUT_CLK_EXT VCC "@inclk[1..0]"

- -- Retrieval info: USED_PORT: areset 0 0 0 0 INPUT GND "areset"

- -- Retrieval info: USED_PORT: c0 0 0 0 0 OUTPUT_CLK_EXT VCC "c0"

- -- Retrieval info: USED_PORT: inclk0 0 0 0 0 INPUT_CLK_EXT GND "inclk0"

- -- Retrieval info: USED_PORT: locked 0 0 0 0 OUTPUT GND "locked"

- -- Retrieval info: CONNECT: @areset 0 0 0 0 areset 0 0 0 0

- -- Retrieval info: CONNECT: @inclk 0 0 1 1 GND 0 0 0 0

- -- Retrieval info: CONNECT: @inclk 0 0 1 0 inclk0 0 0 0 0

- -- Retrieval info: CONNECT: c0 0 0 0 0 @clk 0 0 1 0

- -- Retrieval info: CONNECT: locked 0 0 0 0 @locked 0 0 0 0

- -- Retrieval info: GEN_FILE: TYPE_NORMAL pll_36mhz.vhd TRUE

- -- Retrieval info: GEN_FILE: TYPE_NORMAL pll_36mhz.ppf TRUE

- -- Retrieval info: GEN_FILE: TYPE_NORMAL pll_36mhz.inc FALSE

- -- Retrieval info: GEN_FILE: TYPE_NORMAL pll_36mhz.cmp TRUE

- -- Retrieval info: GEN_FILE: TYPE_NORMAL pll_36mhz.bsf FALSE

- -- Retrieval info: GEN_FILE: TYPE_NORMAL pll_36mhz_inst.vhd TRUE

- -- Retrieval info: LIB_FILE: altera_mf

- -- Retrieval info: CBX_MODULE_PREFIX: ON

Oluşturduğum PLL modülü kompanenti:

- --Copyright (C) 1991-2011 Altera Corporation

- --Your use of Altera Corporation's design tools, logic functions

- --and other software and tools, and its AMPP partner logic

- --functions, and any output files from any of the foregoing

- --(including device programming or simulation files), and any

- --associated documentation or information are expressly subject

- --to the terms and conditions of the Altera Program License

- --Subscription Agreement, Altera MegaCore Function License

- --Agreement, or other applicable license agreement, including,

- --without limitation, that your use is for the sole purpose of

- --programming logic devices manufactured by Altera and sold by

- --Altera or its authorized distributors. Please refer to the

- --applicable agreement for further details.

- -------------------------------------------EDIT------------------

- --&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&

- -- Engineer : Orhan YILMAZ || www.mafgom.com ||

- --&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&

-

- LIBRARY ieee;

- use ieee.std_logic_1164.ALL;

- use ieee.std_logic_unsigned.all;

- use ieee.std_logic_arith.ALL;

-

- package pkg_pll_36mhz_component is

- component pll_36mhz

- PORT

- (

- areset : IN STD_LOGIC := '0';

- inclk0 : IN STD_LOGIC := '0';

- c0 : OUT STD_LOGIC ;

- locked : OUT STD_LOGIC

- );

- end component;

- end package;

Deneme yaptığım top modül (üst modül):

- --=================================================================

- -------------------------------------------------------------------

- -- Orhan YILMAZ

- -- VGA-Top Module

- -- www.mafgom.com

- -------------------------------------------------------------------

- --=================================================================

- LIBRARY ieee;

- use ieee.std_logic_1164.ALL;

- use ieee.std_logic_unsigned.all;

- use ieee.std_logic_arith.ALL;

-

- LIBRARY work;

- use work.pkg_vga_component.all;

- use work.pkg_pll_36mhz_component.all;

- use work.pkg_rgb_array_component.all;

-

- entity vga_top is

- port(

- --Clock,Reset Signal's ports

- clk :in std_logic; -- 50 MHZ

- rst_n :in std_logic;

-

- -- Input Switch RGB value

- i_rgb :in std_logic_vector(14 downto 0);

-

- --Output RGB Signal's ports

- o_red :out std_logic_vector(9 downto 0);

- o_green :out std_logic_vector(9 downto 0);

- o_blue :out std_logic_vector(9 downto 0);

-

- --Output Synchronous Signal's pins

- o_vs :out std_logic;

- o_hs :out std_logic;

- o_clk_pix :out std_logic;

- o_de :out std_logic

- );

- end entity;

-

- architecture RTL_top of vga_top is

-

- signal rst : std_logic := '1';

- signal clk_36mhz : std_logic := '0';

- signal rgb : std_logic_vector(29 downto 0);

-

- signal pos_x : std_logic_vector(10 downto 0);

- signal pos_y : std_logic_vector( 9 downto 0);

-

- signal de : std_logic := '0';

- signal rst_vga_cont : std_logic := '0';

- signal locked_pll_clk : std_logic := '0';

- signal rgb_addr : std_logic_vector(16 downto 0);

- signal rgb_data : std_logic_vector(29 downto 0);

-

- begin

-

- rst <= not rst_n;

- rst_vga_cont <= rst_n and locked_pll_clk;

-

- pll_36mhz_inst : pll_36mhz

- PORT MAP

- (

- areset => rst,

- inclk0 => clk,

- c0 => clk_36mhz,

- locked => locked_pll_clk

- );

-

- vga_cont : vga_control

- port map(

- --Clock,Reset Signal's ports

- clk => clk_36mhz,

- rst_n => rst_vga_cont,

-

- --Input RGB Signal's ports

- i_red => rgb(29 downto 20),

- i_green => rgb(19 downto 10),

- i_blue => rgb( 9 downto 0),

-

- --Output RGB Signal's ports

- o_red => o_red,

- o_green => o_green,

- o_blue => o_blue,

-

- --Output Position value

- o_pos_x => pos_x,

- o_pos_y => Pos_y,

-

- --Output Synchronous Signal's pins

- o_vs => o_vs,

- o_hs => o_hs,

- o_clk_pix => o_clk_pix,

- o_de => de

- );

-

- rgb_data_array: rgb_array

- port map(

- clk => clk,

- rst_n => rst_n,

- i_rgb_addr => rgb_addr,

- i_de => de,

- o_rgb => rgb_data

- );

-

- rgb(29 downto 20) <= (i_rgb(11)&"11"&i_rgb(10)&"11"&i_rgb(9)&"11"&i_rgb(8)) when i_rgb(14) = '1' else (OTHERS => '0');

- rgb(19 downto 10) <= (i_rgb(7)&"11"&i_rgb(6)&"11"&i_rgb(5)&"11"&i_rgb(4)) when i_rgb(13) = '1' else (OTHERS => '0');

- rgb( 9 downto 0) <= (i_rgb(3)&"11"&i_rgb(2)&"11"&i_rgb(1)&"11"&i_rgb(0)) when i_rgb(12) = '1' else (OTHERS => '0');

- o_de <= de;

-

- end RTL_top;

Top modül kompanent:

- -------------------------------------------------------------------

- -- Orhan YILMAZ

- -- VGA-Controler

- -- www.mafgom.com

- -------------------------------------------------------------------

- --=================================================================

- LIBRARY ieee;

- use ieee.std_logic_1164.ALL;

- use ieee.std_logic_unsigned.all;

- use ieee.std_logic_arith.ALL;

-

- package pkg_vga_top_component is

-

- component vga_top is

- port(

- --Clock,Reset Signal's ports

- clk :in std_logic; -- 50 MHZ

- rst_n :in std_logic;

-

- -- Input Switch RGB value

- i_rgb :in std_logic_vector(14 downto 0);

-

- --Output RGB Signal's ports

- o_red :out std_logic_vector(9 downto 0);

- o_green :out std_logic_vector(9 downto 0);

- o_blue :out std_logic_vector(9 downto 0);

-

- --Output Synchronous Signal's pins

- o_vs :out std_logic;

- o_hs :out std_logic;

- o_clk_pix :out std_logic;

- o_de :out std_logic

- ); end component;

-

- end package;

Oluşturduğum testbench dosyası:

- --=================================================================

- -------------------------------------------------------------------

- -- Orhan YILMAZ

- -- VGA-Controler

- -- Testbench

- -- www.mafgom.com

- -------------------------------------------------------------------

- --=================================================================

- LIBRARY ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- use ieee.std_logic_arith.all;

-

- LIBRARY work_top;

- use work_top.pkg_vga_component.all;

- use work_top.pkg_vga_top_component.all;

-

- entity test is

- end entity;

-

- architecture TESTBENCH_VGA of test is

-

- signal clk : std_logic := '0';

- signal rst_n : std_logic := '0';

- signal RGB : std_logic_vector(29 downto 0);

- signal VSYNC : std_logic;

- signal HSYNC : std_logic;

- signal de : std_logic;

- signal clk_pix : std_logic;

-

- begin

- --Generated Clock Signal

- clk <= not clk after 20ns;

-

- --Generated Reset Signal

- rst_n <= '1' after 1000ns;

-

- --

- --VGA_1: vga_control

- -- port map(

- -- --Clock,Reset Signal's ports

- -- clk => clk,

- -- rst_n => rst_n,

- --

- -- --Input RGB Signal's ports

- -- i_red => "1001010101",

- -- i_green => "0010101001",

- -- i_blue => "1010101010",

- --

- -- --Output RGB Signal's ports

- -- o_red => RGB(29 downto 20),

- -- o_green => RGB(19 downto 10),

- -- o_blue => RGB( 9 downto 0),

- --

- -- --Output Synchronous Signal's pins

- -- o_vs => VSYNC,

- -- o_hs => HSYNC,

- -- o_de => de

- -- );

- --

-

- vga_test : vga_top

- port map(

- --Clock,Reset Signal's ports

- clk => clk, -- 50 MHZ

- rst_n => rst_n,

-

- -- Input Switch RGB value

- i_rgb => "100111100000000",

-

- --Output RGB Signal's ports

- o_red => RGB(29 downto 20),

- o_green => RGB(19 downto 10),

- o_blue => RGB( 9 downto 0),

-

- --Output Synchronous Signal's pins

- o_vs => VSYNC,

- o_hs => HSYNC,

- o_clk_pix => clk_pix,

- o_de => de

- );

-

- end TESTBENCH_VGA;

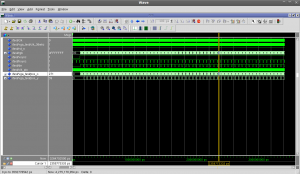

Modelsim ile similasyonunu yaptığınızda aşaüıdakine benzer bir görüntü almanız gerekmekte.(Tıkladığınızda resim büyüyecektir.)

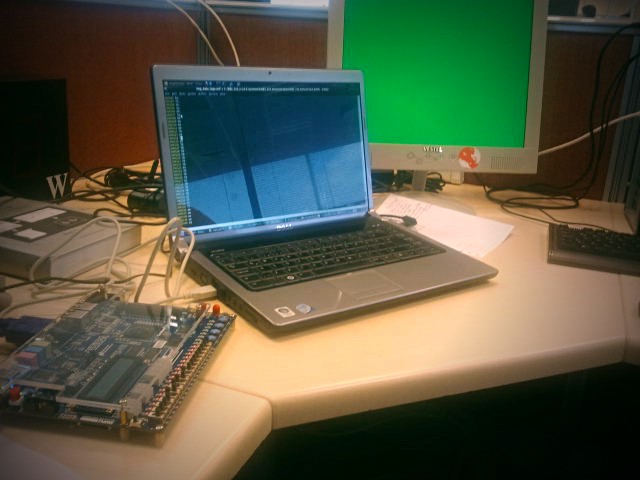

Çalışma görüntüsü:

Eğer farklı bir çözünürlük gerçekleştirmek isterseniz aşağıdaki tablodan yararlanabilirsiniz.

İyi çalışmalar. Takıldığınız yer olursa bana ulaşabilirsiniz.

Kaynaklar:

—————————————

- http://tr.wikipedia.org/wiki/Video_Graphics_Array

- http://tinyvga.com/vga-timing/800×600@56Hz

- http://www-mtl.mit.edu/Courses/6.111/labkit/vga.shtml

- Altera System CD for DE2-115

Son Yorumlar